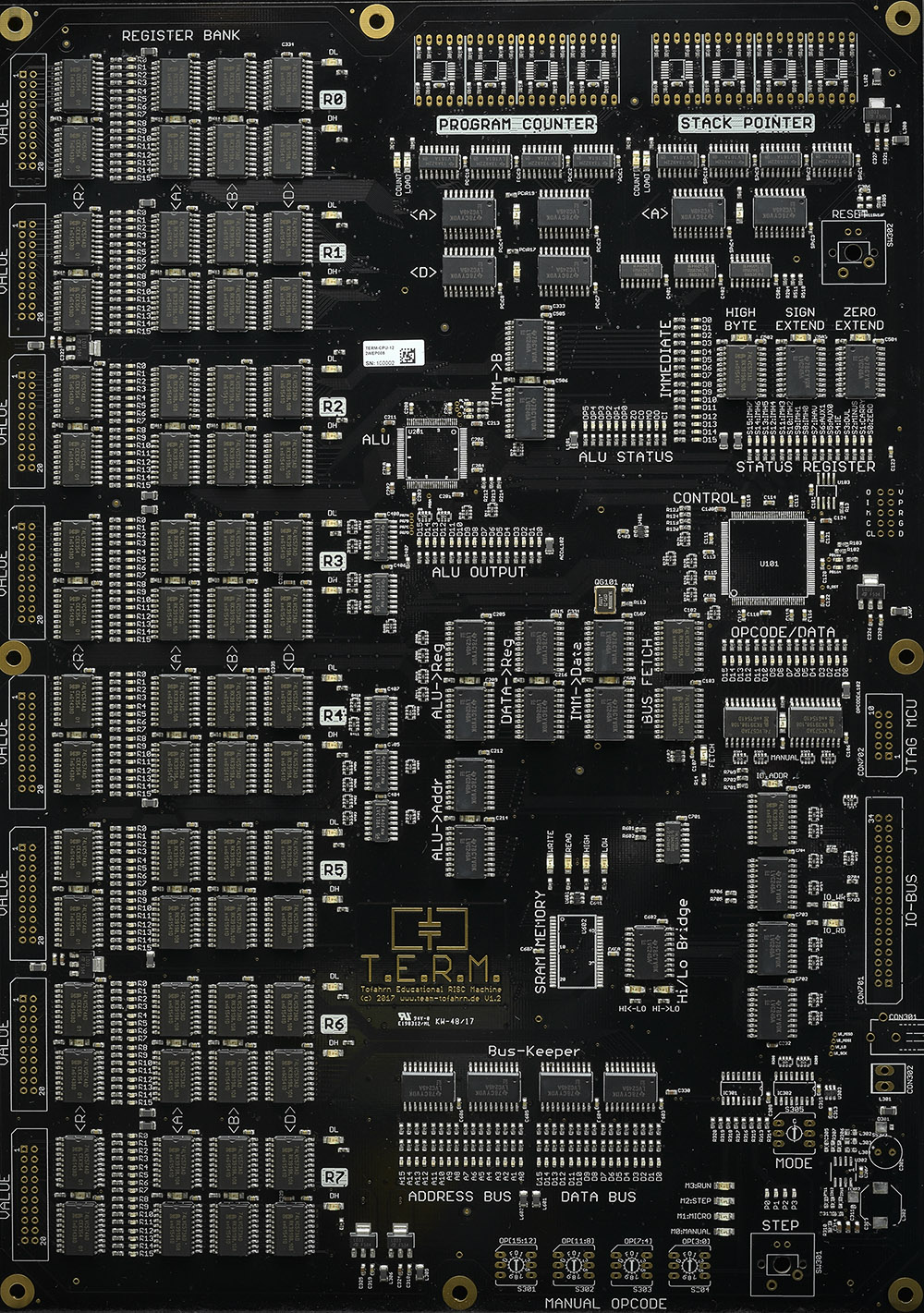

T.E.R.M

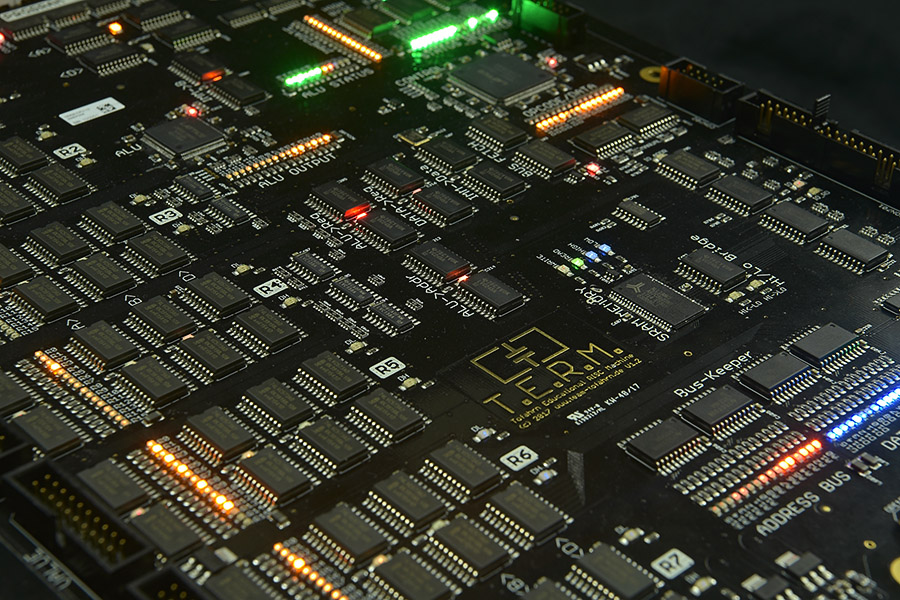

The Tofahrn Educational RISC Machine is a fully functional 16 Bit CPU running at 4 MIPS with most components like the register file, stack pointer and program counter realized with standard logic chips. This allows connecting more than 300 LEDs (314 to be precise) to most data and control lines, which faciliates the visualization of internal data flow and processes.

The arithmetic logic unit (ALU) and the control logic was intentionally placed into two FPGAs to allow for the implementation of different CPU architectures. The current implementation realizes a 16 Bit RISC CPU with constant four clock cycles per instruction (including jump, call, ret and memory accesses) which results in constant 4MIPS (system clock runs at 16 MHz).

The board resembles a Von Neumann architecture and is equipped with an unsegmented 64k x16 SRAM for code and data.

To attach additional components, there is also a 16 Bit IO connector with a separate 8 Bit IO Address space. The IO connection is asynchronous and able to halt the main CPU to slow down IO cycles.

Since processing at 4 MIPS is way too fast to follow internal processes, the execution mode may be switched anytime to single step or even microstep to really follow the data flow instruction by instruction or cycle by cycle. Additionally there is a manual mode, which redirects the CPU command fetch to four hex decoders, so that initial experiments can be made without writing any line of code.

A full toolchain including C/C++ compiler is planned, but currently only provides a (quite powerful) assembler.

The whole project is aimed at the education of scholars and students and is ultimately intended to be an open platform. The current status can be considered successful proof of the concept with first pre-series boards produced.

Just click on a hotspot to get more information.

Feel free to contact TERM@tofahrn.de for more information.